XS-TCAM-104x320:基于FPGA的TCAM开源实现(一)

发布时间:2018-03-06

当前FAST开源项目中通用匹配引擎(GME)规则匹配能力有限,只支持64条规则长度为512比特的带掩码匹配功能,对需要大量规则匹配的环境,只能采用片外的TCAM器件。

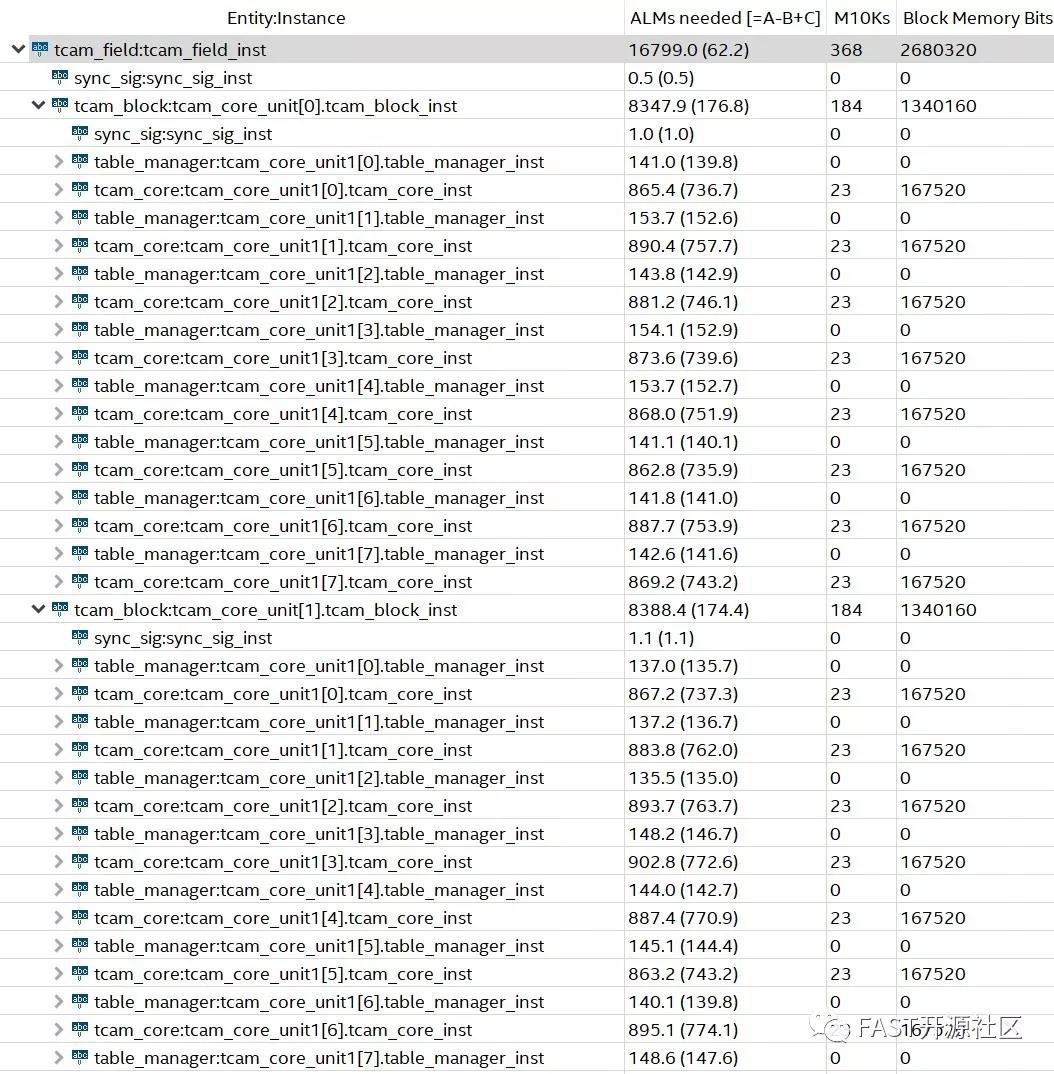

为此,湖南新实网络科技有限公司基于FPGA内部的查找表逻辑和RAM资源,设计实现了具有TCAM功能的IP核——XS-TCAM-104x320。目前XS-TCAM-104x320 IP的源代码已经开源,对提升FAST流水线查表引擎的能力具有重要意义。

一、XS-TCAM-104x320的基本指标

目前实现的指标:

1.编译速率:125Mhz

2.规则条数:320条

3.LUT资源:16799

4.RAM(M10K)资源:368

5.查询周期:首次单条规则查询12周期出结果,后续连续查询则1个时钟周期出结果。

二、XS-TCAM-104x320的实现原理

针对FAST前期版本支持流表项条目少的不足,目前对查找算法进行了改进,实现了XS-TCAM-104x320 IP,其优点如下:

1.支持按优先级查找匹配;

2.支持硬件进行规则更新;

3.支持规则条目的按需扩展;

4.支持匹配域关键字的按需扩展;

5.支持规则查找/更新按掩码匹配;

6.采用流水化并行的处理方式可实现高速查找匹配。

1、设计思想:

XS-TCAM-104x320 IP使用二维数组的存储方式,并行的进行规则更新及查找匹配,并采用流水化的方式实现多条规则匹配查找,从而实现高效快速的分类查找的目的。另外,此算法支持灵活的匹配域及流表表项的扩展能力,可满足将来匹配域扩展及流表表项扩展的需求。

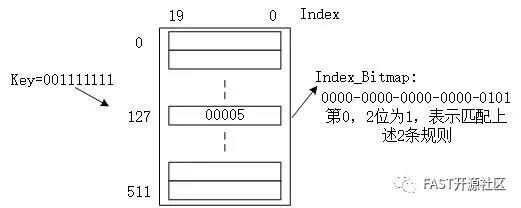

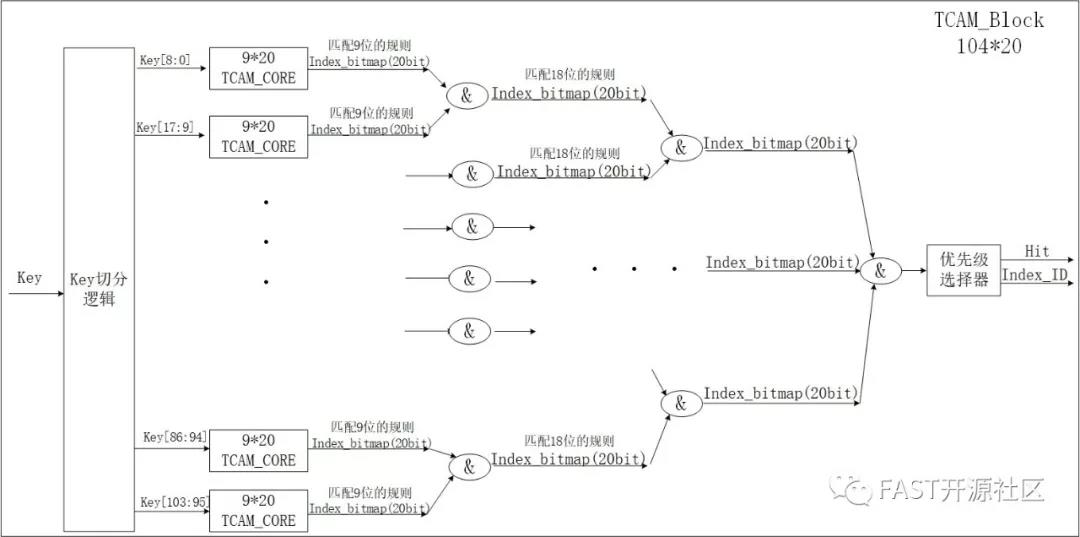

XS-TCAM-104x320 IP是基于FPGA每个内嵌RAM块可配置成512*20的双端口RAM进行的实现,图1为XS-TCAM-104x320 IP基本处理结构图,由于RAM块为512*20因此切分的匹配域关键字(Key)为9位,查找逻辑以9位Key为查找地址对表项进行访问,得到20位的规则索引标识位,优先级选择器则根据优先级输出最高优先级的规则索引。此算法将索引0位的规则定义为最高优先级的索引位。

图1 XS-TCAM-104x320 IP基本处理结构图

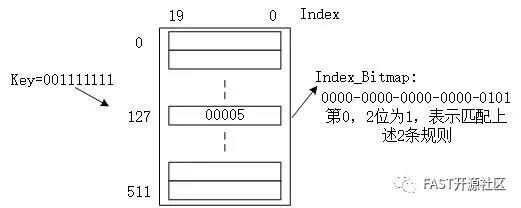

参照图2,图2为流表匹配域的存储结构图,其为512*20的RAM存储块,在此可视为512*20的二维数组,其中行地址512个,为匹配域关键字(Key)字段;列地址为20个,为规则索引字段(Index)。图2将9位的Key作为地址查找RAM(Key=00111_1111),查找出的结果为此关键字段命中的20条规则的索引标识位(Index_Bitmap)为0_0005,其中第0,2,位为1,表示该key匹配了上述2条规则。由于0为高优先级位,因此0号索引被输出。

图2 流表匹配域存储结构图

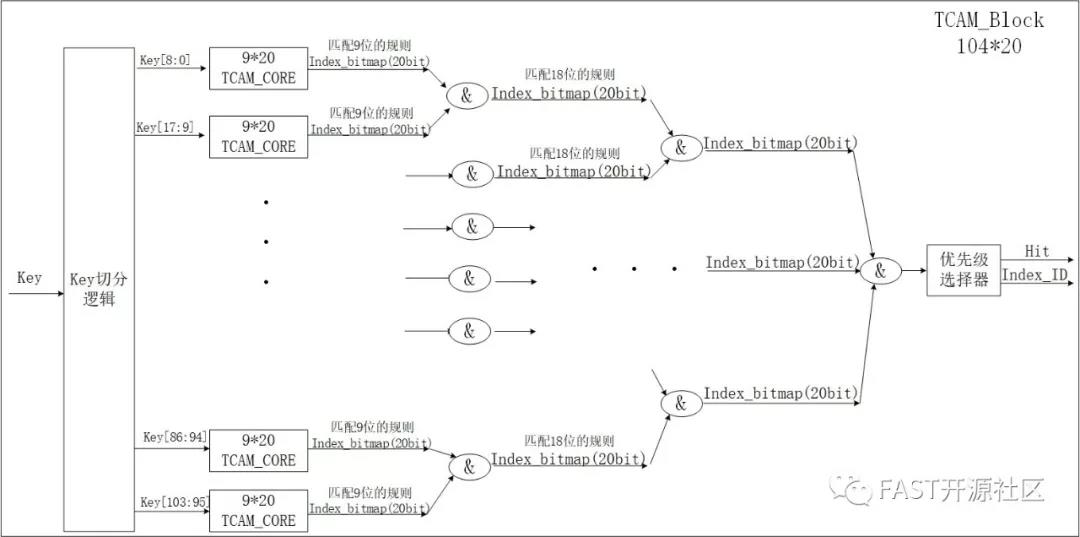

2、规则长度扩展

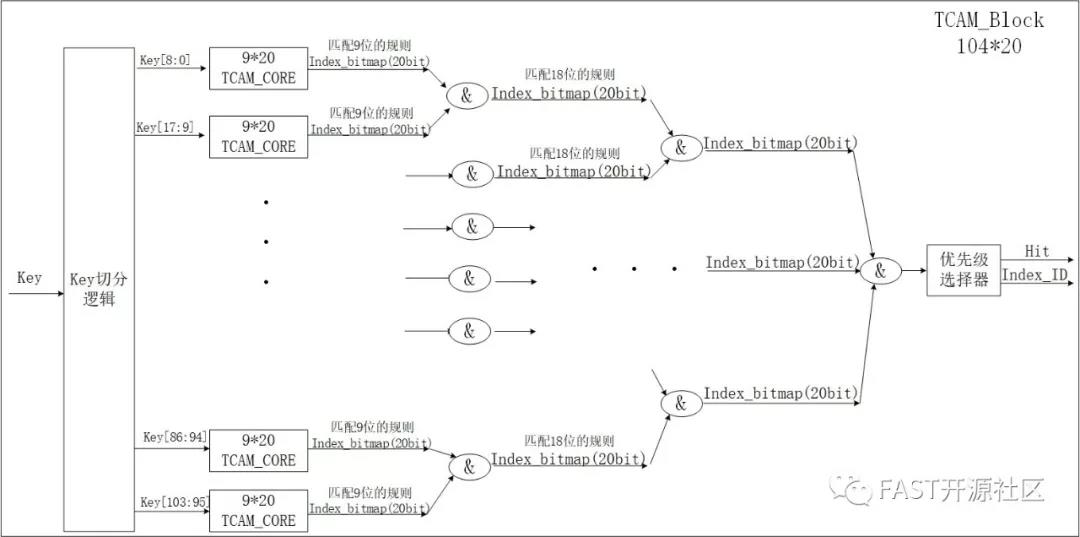

对于104位的五元组信息,需12个9*20TCAM_CORE即可实现,输出的bitmap进行比特与即可得到匹配的bitmap,如图3所示;

图3 规则长度扩展到五元组处理流程图

最后,通过优先级选择器选择优先级比较高的索引输出。

3、规则数目扩展

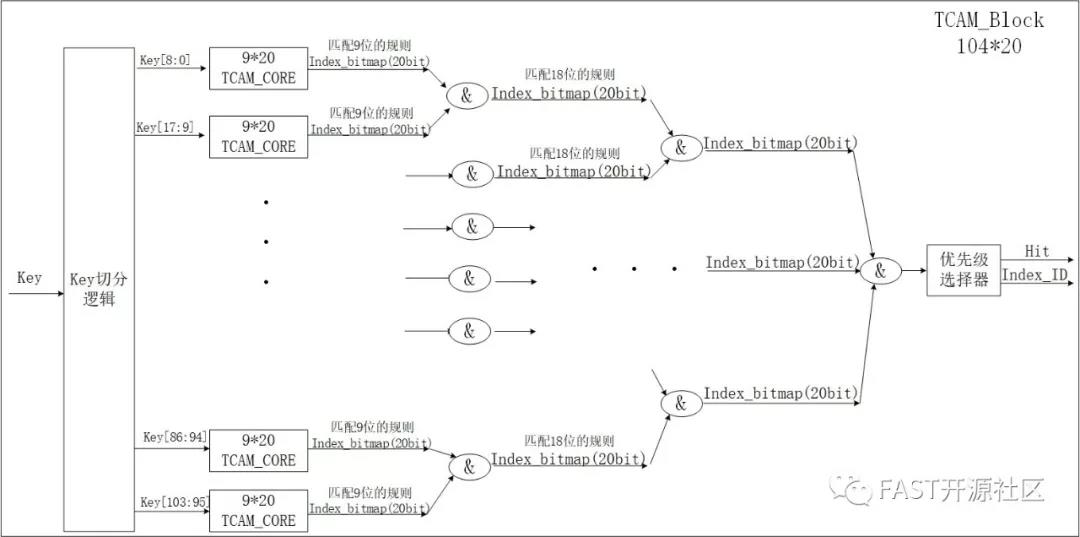

通过TCAM_Block模块可以实现规则数目的扩展,如图4所示,通过将不同的规则对应到不同TCAM_Block模块的Bitmap中,则可以并行的扩展规则的数目。通过此方式在资源允许的情况下可以无限制的扩展。

图4 规则扩展结构图

目前基于Altera A5 FPGA 的FAST架构只实现的320条规则,若用户需要更多表项即可按需扩展。

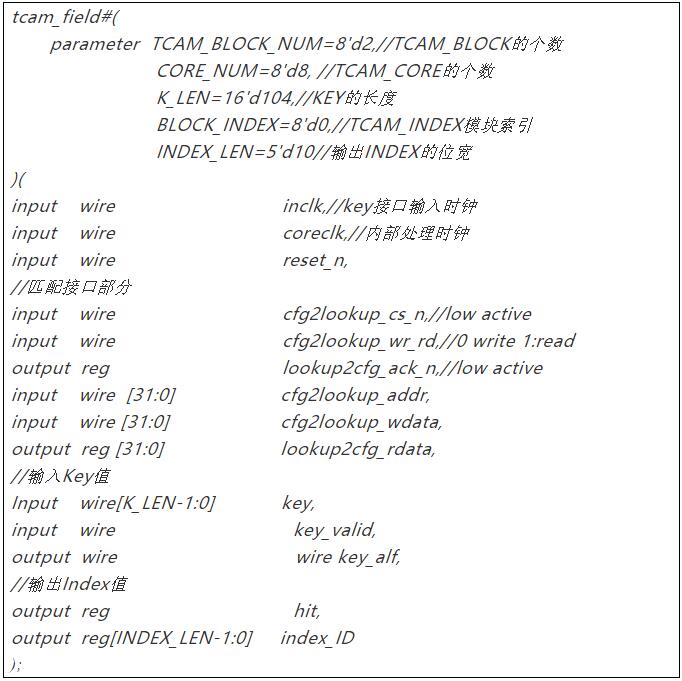

三、XS-TCAM-104x320的代码说明

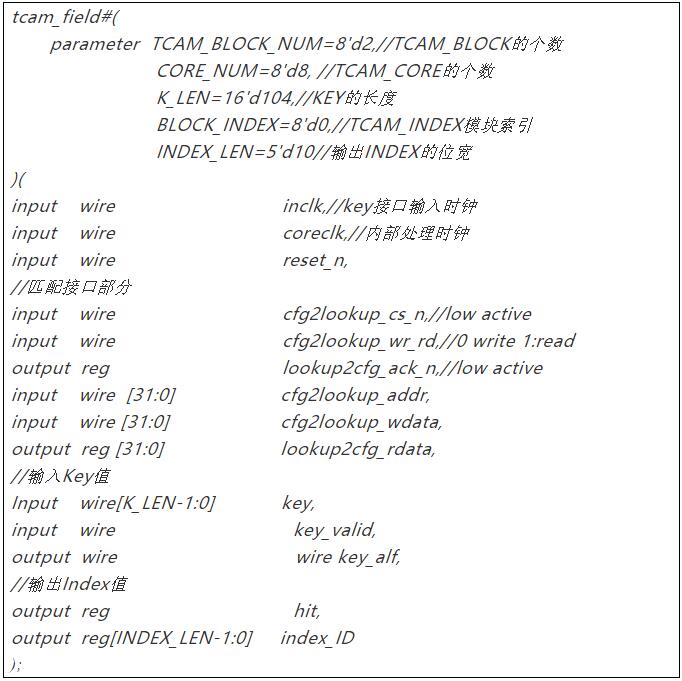

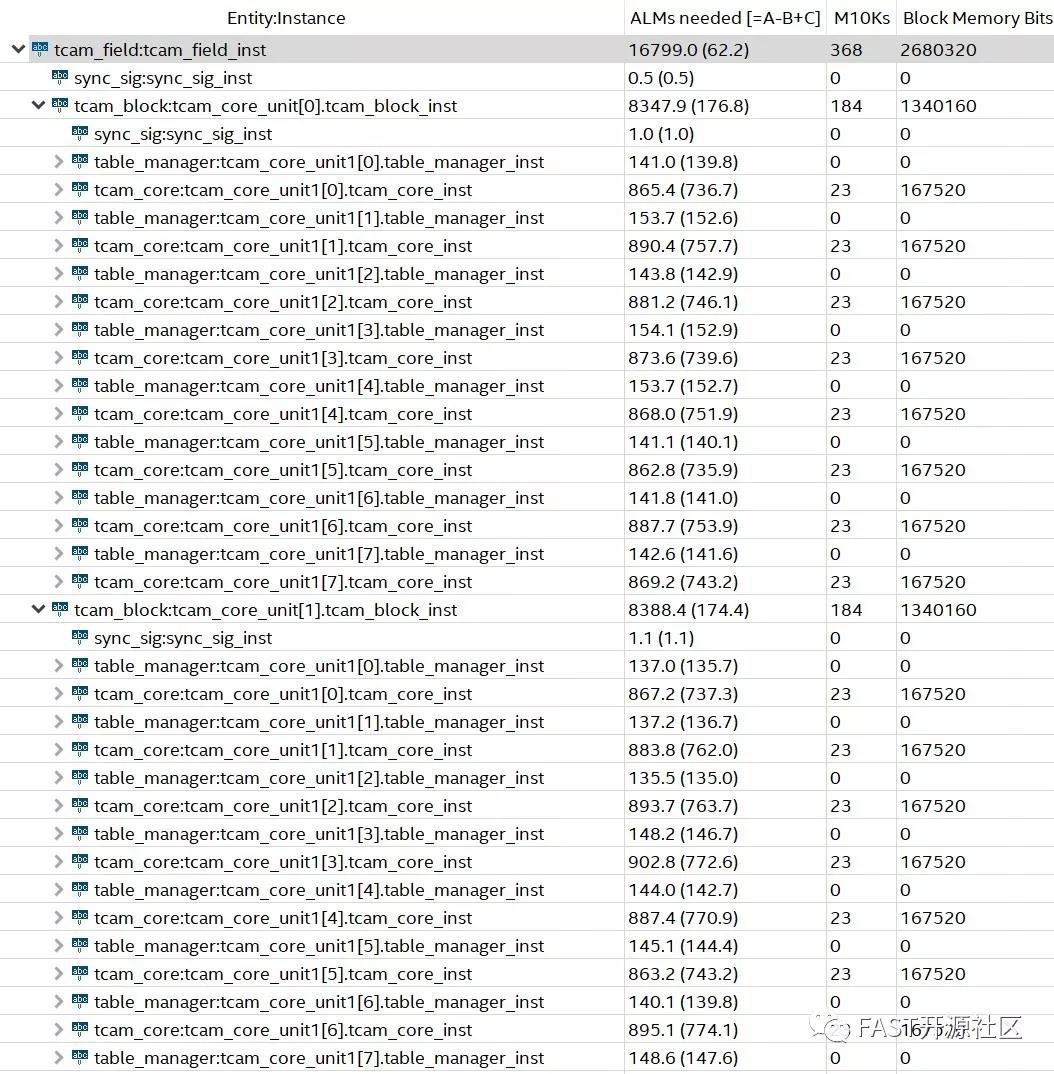

以下为XS-TCAM-104x320的顶层代码其主要分为四部分:时钟复位接口、规则配置接口、匹配关键字Key输入接口以及规则输出索引号Index_ID具体如下图5所示,其Quartus II 中代码结构如图6所示,代码文件如表1所示。

图5 XS-TCAM-104x320 IP顶层接口图

图6 XS-TCAM-104x320的代码结构

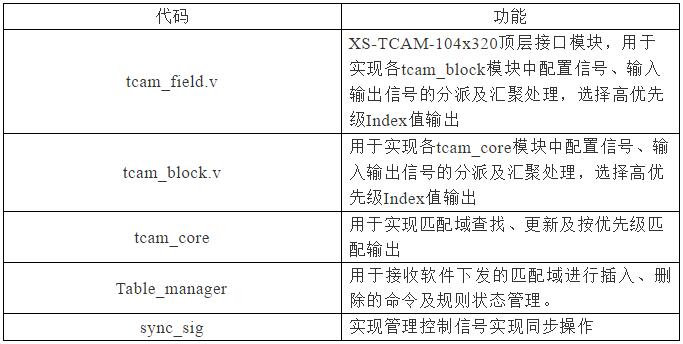

XS-TCAM-104x320的代码文件说明如表1所示:

目前XS-TCAM-104x320已经完成调测试,在FAST未来发展规划中,XS-TCAM-104x320将作为重要的改进特性加入到FAST流水线的GME中。我们后续将对XS-TCAM-104x320的使用方法进行进一步介绍。

目前XS-TCAM-104x320 IP代码可访问www.fastswitch.org,选择“代码”选项卡,点击FAST UM,点击如下按钮开始下载: