“我OpenBox又回来了!”

沉寂了16个月,终于又提笔开始写《硬件二层交换设计与实现》。从软件设计到硬件设计需要这么长时间吗?答案是肯定的,不仅需要,而且这点时间还只能初入Verilog代码编程之门。

但从网络实验教学的角度来看,这是不可接受的。故我们想换个思路,走走捷径。然而这一走,便走了整整16月有余。

所幸略有小成,与君分享,共勉自学、自研、自证之艰辛与快乐。

A)P4与Tofino

书上或网上能找到的内容请大家自行查找了解。见:https://p4.org

B)FAST全软件可编程平台

FAST架构在我们之前的文章中有介绍,该平台也是一种典型的SDN架构设计,硬件数据平面主要包括FPGA OS和UM两部分,核心逻辑处理在UM模块中。UM又分成了5个不同逻辑功能流水线,

用户可以针对此流水线进行改造升级或扩展新的流水级功能。然而,使用Verilog语言来开发FPGA芯片功能着实是一件比较有难度的事情,至少在成为一个合格的Verilog代码工程师之前来说,确实有比较漫长和艰辛的路程要走。

受P4编程思想的启发,我们决定将FAST架构中的UM部分更换成具备P4开发能力的硬件逻辑部件。故该平台依然采用多核CPU加FPGA架构,P4逻辑全采用FPGA编写,所有功能和指令逻辑全在硬件实现。

C)基本功能

1.分组前96字节内,小于128的任意bit位,任意多个PHV对象定义;

2.支持32字节Metadata对象编程,含16字节用户自定义Metadata内容;

3.分组前60字节内,任意bit位对象查表匹配,精确匹配与带掩码匹配,匹配字段支持输入端口等Metadata字段;

4.每动作支持14条指令,支持加、减、与、或、异或、取反等操作;

5.每个指令执行器中含16个临时寄存器,支持临时变量暂存与读取,位宽支持1到64位;

6.支持有状态的存储寄存器对象定义与操作,存储寄存器位宽支持1到64位,最大个数支持128个。支持多个寄存器对象编程;

7.支持对分组进行协议插入与删除,长度支持1到16字节;

8.动作与指令均支持参数化配置,即可运行前实例化,也可运行时调整;

9.支持32种不同逻辑业务处理功能在线编译、在线加载、在线配置、在线卸载,不影响其他业务逻辑;

10.提供P4后端编译器,支持用户P4代码编译;

11.提供P4运行时配置管理工具,支持用户流表配置、动作配置和寄存器初始配置。

拥有上述平台编程功能后,对硬件的设计要求便会变得较为简单。原来要花较长时间,写较多代码的功能,现在可以简单、快速的实现。

A)设计原理

从交换机的几个功能步骤开始,先实现源MAC地址的学习。从平台功能分析,使用寄存器部件比较合适。

拟定义一个端口与MAC地址的映射表,存储在寄存器对象中,使用源MAC地址作为寄存器对象的索引,分组输入端口号作为该索引位置的值。在使用目的MAC查表时,亦使用MAC地址作为索引进行查找,即可获取该地址学习存储的端口号。

由于MAC地址为48位,本平台支持寄存器的深度有限,故本案例中仅取MAC地址的后4位作为索引。故实验演示时,要求测试主机的MAC地址尾数不同。

单播地址可以采用上述思路进行设备,那组播与广播地址呢,我们本案例拟采用全泛洪的方式先来实现一个基础版本。

想要做组播功能可以将组播协议配置规则送CPU处理,CPU学习到入组和退组信息后,通过P4的运行时工具进行组播MAC与相应端口号的规则配置即可。

B)代码实现

action learn_forward()

{

MAC_PORT.regwrite((u8)hdr.eth.smac&0xF,std_meta.ioport);

std_meta.ioport = MAC_PORT.regread((u8)hdr.eth.dmac&0xF);

}

单播自学习与转发

action mb_cast()

{

MAC_PORT.regwrite((u8)hdr.eth.smac&0xF,std_meta.ioport);

std_meta.ioport = ~std_meta.ioport;

}

多播泛洪

以上为硬件二层交换机(原型系统)全部业务逻辑功能代码。是的,就是这四行代码!!!!

A)软件核心代码

B)编译器结果

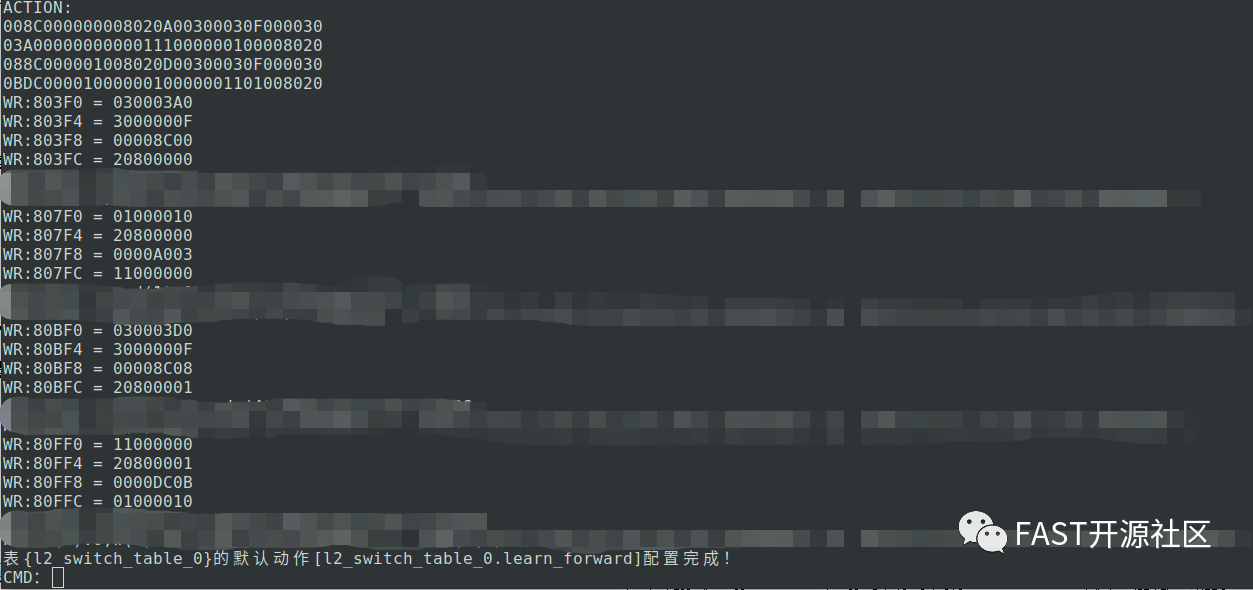

C)硬件配置

D)Ping通测试

C:\Users\Administrator>ping 192.168.1.198

正在 Ping 192.168.1.198 具有 32 字节的数据:

来自 192.168.1.198 的回复: 字节=32 时间<1ms TTL=127

来自 192.168.1.198 的回复: 字节=32 时间<1ms TTL=127

来自 192.168.1.198 的回复: 字节=32 时间<1ms TTL=127

来自 192.168.1.198 的回复: 字节=32 时间<1ms TTL=127

物质守恒、能力守恒,苦难亦然守恒。

为了让学生们在我们平台编写硬件逻辑少些痛苦,我们艰苦奋斗了16个月,对P4的原理、代码和编译器进行了仔细琢磨、分析和领悟。我们认为P4是一门较为优秀的编程语言,更是一种硬件编程的创新思路和具体表达形式。我们无法去破解P4的硬件实现,固然也无从参考,而是领悟P4编程方式的精髓理念后,采用了原有FAST架构和部分逻辑调整,并配置P4后端编译适配,打造了现如今的支持P4的FAST架构可编程平台。

本平台结合了FAST架构与P4可编程的双重优势。支持用户在最底层硬件到最高层软件全方便的编程与验证,而且编程语言均使用C语言和类似C的P4语言,进一步降低了学习与使用难度。

下一步,做个硬件路由器?或者您有更美好的想法,我们可以试一试!

有需要开发可编程硬件(FPGA、ASIC等)的P4后端编译器,或获得本平台介绍相关源码的客户,请与15116127200(微信同号)联系,阅读更多FAST相关文章请进入以下公众号。